Power9プライムから見えてくる、来たるPower10でのメモリーの機能強化

IBMのLinux on Power Systemsハードウェアを導入しようとしている顧客は、IBMがPower9'プロセッサーの出荷準備を進めていることから、もうすぐ非常に大きなメモリー帯域幅の増強の恩恵を受けられることになりそうです(「Power9'」の「9」の後ろはプライムまたはダッシュ記号であり、アポストロフィでも誤入力でもありません)。 2018年3月のプレビュー記事に記したように、Power9'チップは、一般的には各種のシステムとアクセラレーターのインターコネクトに使用されている新しい高速なSERDESシグナリング テクノロジーが備わり、メモリー バッファーそして、DDR4および将来のメモリーをサポートするための調整が施されるなど、大幅にアップグレードされたメモリー サブシステムが特徴となっています。

Power9'プロセッサーが、IBM自身の手によるIBM iおよびAIXオペレーティング システムを稼動できない技術的な理由はありませんが、Power9'で稼働する主要なオペレーティング システムとなるのは、IBMの新たなRed Hat Enterprise Linux(商用Linuxディストリビューターを買収したおかげです)ということになるようです。この点について触れるのには理由があります。IBMが現在提供しているよりも実際にもっと多くのメモリー帯域幅を必要とするIBM iまたはAIXアプリケーションを使用しているのだとしたら、2021年にPower10ハードウェアが登場するまでの期間を乗り切ることができるようにするRPQシステムについて、検討ぐらいはしてみた方がよいと思われるからです(Power10は2021年の初めではないかと見ています)。

新たなPower9'メモリー サブシステムは、IBMがOpenCAPI Memory Interface(略してOMI)と呼んでいるものに準拠しています。同社のPower SystemsアーキテクトのJeff Stuecheli氏と、Power9'プロセッサーのエンジニアのScott Willenborg氏が、先日、スタンフォード大学で開催されたHot Chipsカンファレンスで、新たなOMIメモリーについてプレゼンテーションを行いました。そのプレゼンテーションで示された、IBMがメモリーに関してPower9'チップでどのようなことを行ってきたかについて、またそのことからPower10プロセッサーに関してどのようなことが予想されるのかについて紹介しようと思います。

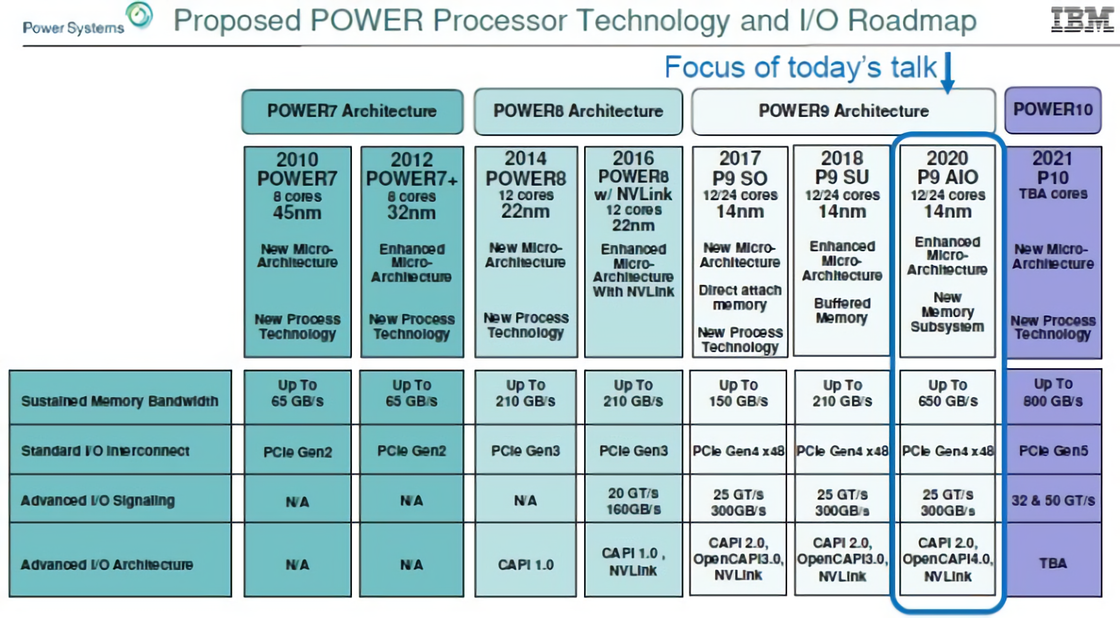

まずは、この10年の間にIBMのPowerチップに実装されたメモリーおよびI/Oについて見直してみましょう。次の表をご覧ください。

IBMは長い間、Powerチップでバッファード メモリーを使用してきましたが、そのことこそが、同時期に利用可能だった代表的なX86プロセッサーに比べてソケット当たりでより多くのメモリーを接続でき、また、当時の競合するX86で高帯域幅向けに使用されていたメモリーに比べて概して動作がはるかに低速なメモリーを使用していても、より多くのメモリー帯域幅を実現できていた理由の1つと言えるでしょう。「Centaur」メモリー バッファーは、それぞれ2014年および2016年に発表されたPower8およびPower8'プロセッサー向けに設計されました。これらのメモリー バッファーの特長については、以前の記事で取り上げたことがあります。上の表に示されているように、Power7およびPower7+チップは、持続メモリー帯域幅はたったの65GB/秒(STREAMメモリー帯域幅ベンチマーク テストで測定)と、かなり低速でしたが、Power8およびPower8'(PowerアーキテクチャーにNVLinkを追加してNvidia Tesla GPUアクセラレーターをPowerコンピュート コンプレックスに直接アタッチできるようにした改良版)チップでは、ソケット当たりの持続メモリー帯域幅は210GB/秒でした。

Power9プロセッサーでは、IBMはプロセッサー ラインを2つに分けました。1つは、DDR4メモリー コントローラーがチップ上にエッチングされ、そのためDDR4メモリーを直接駆動できるスケールアウト バージョンで、上の表の「Nimbus」P9 SOチップがそれです。Centaurメモリー バッファー チップは、上の表の「Cumulus」Power9 SUチップのアーキテクチャーに引き継がれましたが、ご覧のように、Power9 SOチップではCentaurバッファーを捨てたことで、ソケット当たりの持続メモリー帯域幅は29.6%減の150GB/秒となりました。一方、Power9 SUチップのメモリー帯域幅は210GB/秒のままです。ちなみに、これは、Intelがファットな「Skylake」または「Cascade Lake」Xeon SPプロセッサーで可能になるもののほぼ2倍です。

Power9'およびPower10チップでは、OpenCAPIメモリーのおかげで、ソケット当たりのメモリー帯域幅は急増することになります。ただし、単に高くなるというだけでなく、1年半前のIBMの計画と比べても大幅に高くなりそうです。当時の計画では、Power9'のシングル ソケットの持続メモリー帯域幅は350GB/秒と見込まれていました。それはそれとしてかなり衝撃的だったのですが、OpenCAPIメモリーの完成を踏まえて、さらに驚異的な650GB/秒にまで引き上げられています。Power10チップについては、1年半前の計画では、OpenCAPIメモリーによって、最大435GB/秒の持続メモリー帯域幅を実現するとされていましたが、最新のロードマップでは、800GB/秒へと引き上げられています。

ちなみに、このメモリー帯域幅は、Nvidia Tesla GPUアクセラレーターが積層High Bandwidth Memory(HBM2)で得ることができるほぼ同じレベルであり、これは、数多くのアプリケーションでのコンピュート バランスをGPUからCPUへといくらか戻させることになるかもしれません。あるいは、少なくともある種のパワー バランスや、ハイブリッドCPU-GPUマシンのエンジニアリングにおけるバランスには影響を及ぼすかもしれません。

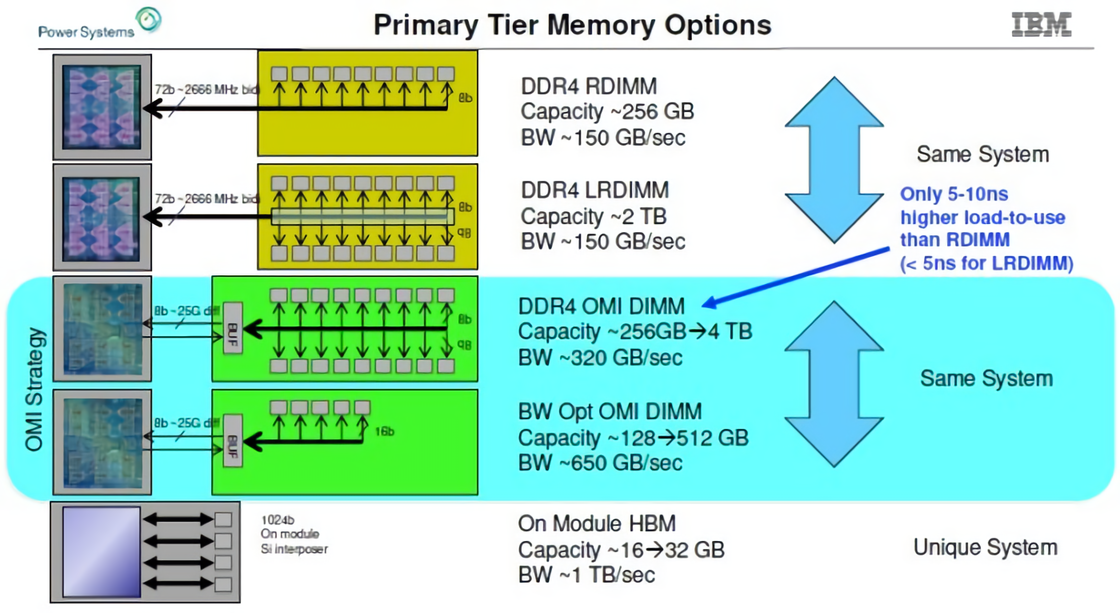

それでは、IBMはどのようにしてそれを行うのでしょうか。以下の図を参照しながら見て行きましょう。

Power9チップ上にダイレクト アタッチされたメモリーでは、メモリー信号は72ビット幅(64を超える余分のビットはエラー訂正用)で、2.67GHzで動作します。Registered DIMMは容量が少ないため、Power9ソケットは約256GBが上限で、持続帯域幅は150GB/秒です。Load Reduced(負荷低減)DDR4メモリー スティックでは、帯域幅は同じですが、このメモリーはDIMMで積層できるため、ソケット当たりの容量は2TBまで引き上げることができます。

Power9'プロセッサーでは、IBMはバッファード メモリーを使用しますが、チップ サプライヤーのMicrochip社によって製造されるはるかに小さいメモリー バッファーへ切り替えることになります。これは、IBMのCentaurチップに比べてはるかに小さく、IBMがPower Systemsハードウェア向けに構築しているものよりはるかに小さいメモリー カードが可能になります(詳細については後述します)。Power9'チップにおけるSERDESは8ビット幅であり、差動信号は25.6GHzで動作します。エンコーディングのオーバーヘッドを除いた後では25Gb/秒ということになります。

OpenCAPIメモリーおよびそれに先行するDMIメモリーでは、メモリー容量と帯域幅との間に相互作用があり、IBMはPower9'チップで2つの異なるオプションを提供する予定です。通常のOpenCAPI DDR4メモリー スティックの場合、容量はソケット当たり256GB~4TBで、帯域幅は約320GB/秒となります。これはほぼIBMが1年半前に可能だと述べていた通りです。しかし、バッファーからの接続を共用してメモリーの容量を少なくするオプションもあり、その場合、容量は1ソケット当たり128GB~512GBに減少しますが、ソケット当たりの帯域幅は650GB/秒と、おおよそ倍になります。特に、バッファーなしのRDIMMまたはLRDIMM DDR4メモリー スティックと比べて、OpenCAPI Memory Interfaceではおよそ5ナノ秒~10ナノ秒のオーバーヘッドが加わるだけであることを考えれば、これはフェアなトレードオフと言えるでしょう。HBM2メモリーのメモリー インターフェースは、1,024ビットと非常に広く、帯域幅は1TB/秒にまで引き上げることができますが、容量は約16GB~32GBであり、これはCPUベースのシステムのメイン メモリーとしてはまったく実際的なサイズとは言えません。

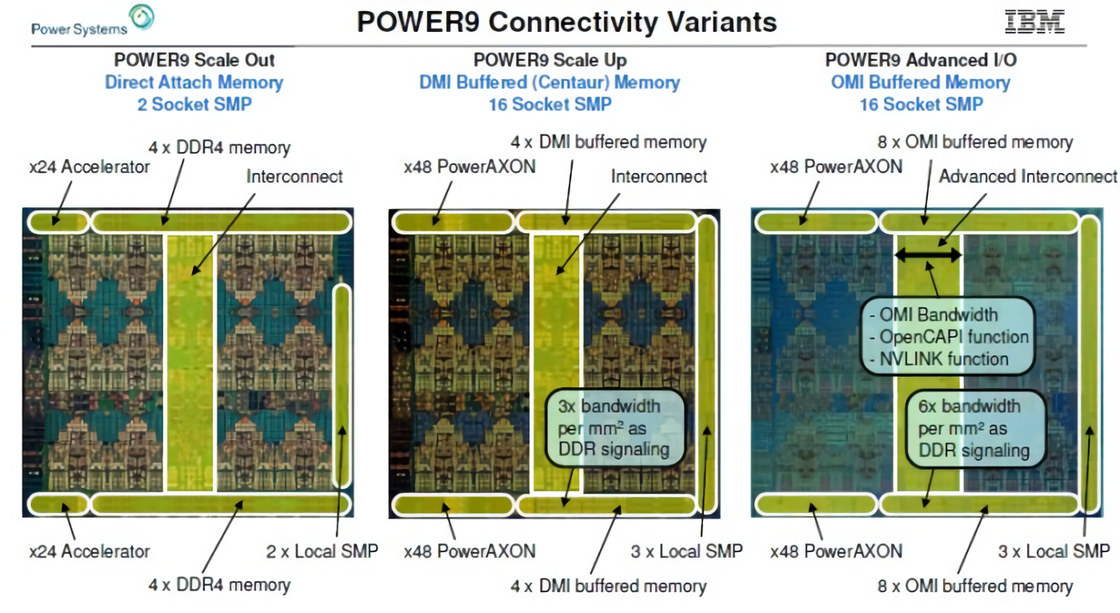

以下は、メイン メモリー アタッチを含め、各種I/Oの点からの、これらのPower9プロセッサーの比較を示したものです。

Power E950およびPower E980システムで使用される「Cumulus」Power9 SUチップには、25Gb/秒で動作する48レーンのバンク2つから成る、96レーンのBluelink I/O(現在はPowerAXONと呼ばれている)がチップに組み込まれています。また、このチップには、4つのDirect Memory Interface(DMI)SERDES(シリアライザ/デシリアライザの略)のバンクも2つあります。それの帯域幅は、「Nimbus」Power9 SOプロセッサーで使用されているDDR4コントローラーで使用されるシグナリングの3倍(チップ面積当たり)だとIBMは指摘しています。これが重要なのは、DMI SERDESを使用することによって、IBMがBluelink SERDESのために追加する余地が大きくなるからです。上の図に示されているSMPリンクは実際にはNUMAリンクであり、16Gb/秒で動作します。これはBluelink SERDESに比べて実際、低速であり、奇妙なことですが、NUMAはそれ以上を必要としないようです。

Power9'プロセッサーでは、IBMには、拡張されたOpenCAPIメモリーSERDESがありますが、これは帯域幅を倍にすることができ、しかも同じ差動信号を使用して同じく25Gb/秒で動作します。これが、メモリー帯域幅がさらに増えるのを可能にしているものです。

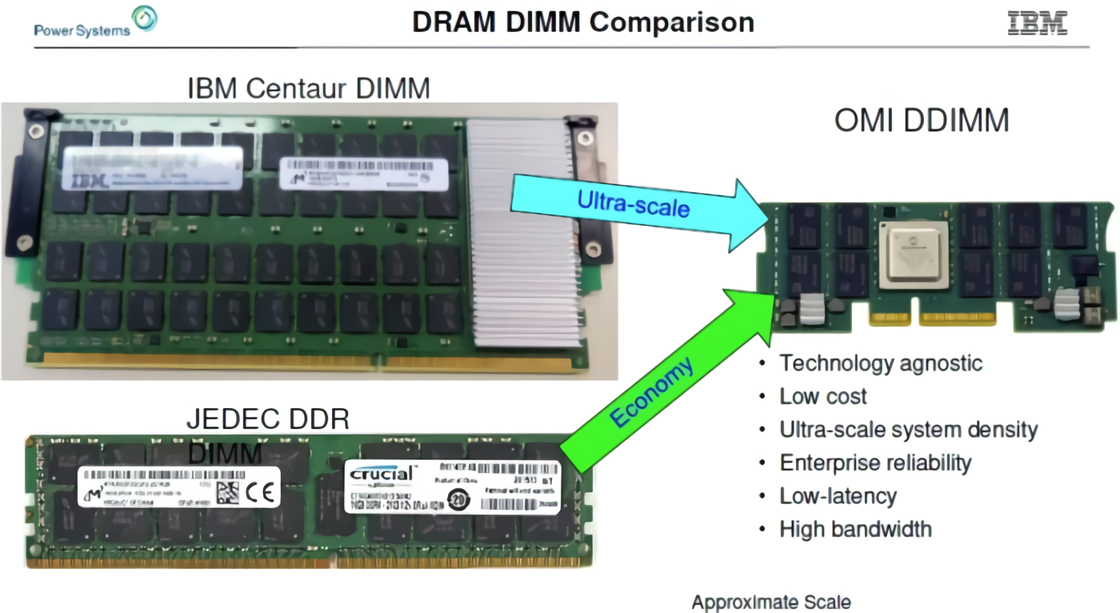

以下は、IBMのCentaur DIMMおよびJEDECメモリー規格に準拠した通常のDDR4 DIMMと、OpenCAPIメモリーとの比較を示したものです。

Microchip Smart Memory Controller 1000は、JEDEC DDR5メモリー規格に先行するOpenCAPI Memory Interfaceを実装するように設計されています。JEDEC DDR5メモリー規格では、IBMおよびIntelが長い間ハイエンド システムでバッファード メモリーを使用してきたのと同じ理由で、メモリー バッファーをこのアーキテクチャーに追加することが見込まれています。DIMMにより多くのメモリーを追加し、かつ、モジュール当たりの帯域幅を増加するには、そうするしかありません。OpenCAPI Memory InterfaceがJDEC規格の上位集合であるかどうか、互換性がないのかどうかは定かではありませんが、IBMが開発してきたアイデアが採用されることになるのは確かです。ちょうど、CAPI(PCI Express 3.0および4.0トランスポート上で動作)やOpenCAPI(25Gb/秒のBluelink SERDES上で動作)によって、IntelのCompute Express Link(CXL)アクセラレーター アタッチ プロトコルおよびトランスポートが触発されているのとよく似ています。Power9'チップにおけるOMI SERDESは、25Gb/秒で動作するチャンネル当たり8レーンの16チャンネルのメモリーで、最大650GB/秒の持続帯域幅を実現でき、一方、Microchip SMC 1000 DDR4メモリー バッファーは最大で410GB/秒の持続帯域幅に達します。

Power10チップでは、PowerAXONおよびOMI SERDES(いずれもBluelinkをベースにしています)には、32Gb/秒および50Gb/秒のネイティブ シグナリングがあり、IBMがPower10プロセッシング コンプレックスでどのようにそれらを利用するかに応じて、さまざまな形でのパフォーマンス向上が組み合わさって提供されることになります。32Gb/秒のシグナリングは、おそらく、より大きいバッファー チップで、DDR5メイン メモリーでのOMI SERDESに使用されることになるようです。そのためIBMが各Power10ソケットで提供することを予定している800GB/秒の処理が可能です。また、OMIチャンネルの数は、それぞれが8レーンの16で同じままであり、25Gb/秒ではなく32Gb/秒での動作となるものと思われます。Bluelink SERDESは50Gb/秒へ倍増されるようです。また、これらのデバイスでOpenCAPI 5.0プロト/コルがサポートされ、おそらくNVLink 3.0ポートも同様でしょう(IBMはそうは言っていませんが)。また、IntelのCXLプロトコルもこれらのインターコネクト サーキット経由でサポートされるのではないかと思われます。IBMはPower10でBluelinkレーンの数を増やすようには思われません。Power9やPower9'と同じく、おそらく2つのバンクで96レーンのままでしょう。

我々が知る限りでは、Power10チップはSMT4で48コア、SMT8で24コアとなるようですが、IBMはこれについて正式に発表していません。