Power11のトランジスタ数の食い違いについての説明のようなもの

Power11の発表に関して不可解なことの1つは、Power10およびPower11サーバー チップのロジックおよびキャッシュ デザインの違いは大きくないのにもかかわらず、Power10からPower11で、トランジスタ数がほぼ2倍に増加したように思われることです。

どういうことなのかよく分からなかったので、 7月上旬のPower11の発表の際にも、そのように述べていました(トランジスタ数の食い違いについて注目したのは、Power11に関する最初の記事が掲載された後 、Power11 Redbooksのドラフトを入手してからのことです)。Redbooksに掲載されている表には、Power11チップのトランジスタ数は300億個で、クロック スピードは3.8 GHz~4.4 GHz、ダイ サイズは654 mm2 と記されています。また、Redbooksによれば、Power10チップのトランジスタ数は180億個で、クロック スピードは3.75 GHz~4.15 GHz、ダイ サイズは602 mm2 だということです。ただし、Power11のトランジスタ数についても、180億個と記載している箇所があったように思います。

Power11ダイで増えた52 mm2 分のチップ面積が何のためのものなのかはよく分かりませんが(それについては尋ね忘れていました)、Power10およびPower11プロセッサーのチーフ アーキテクトで、IBMのPowerチップの多くの世代の設計に携わってきたBill Starke氏に解説してもらえる機会を得ることができました。

結局のところ、IBMはこれまで、業界の他の会社がそうしてきたのとは異なり、PowerおよびSystem zチップでデバイス内のすべてのトランジスタ数をカウントしてきたわけではなかったということです。

「私たちには、極めて独自のツールによる作業フローがあります」とStarke氏は『 The Four Hundred』に述べています。「たとえば、あなたのトランジスタ数のカウント方法は、あなたのツールの作業フローから生み出されたものだと思います。私たちがこれまでカウントしていたのは、システムでアクティブおよび論理的に数字の0と1を表現するトランジスタの数でした(実際のシステムの機能ロジック)。しかし、このような半導体を作っているときにも、別の形で使用されているトランジスタが他にもたくさんあります。たとえばSpyre AIチップで、業界標準の作業フローを使用し始め、その時点で公開されていたSpyreのトランジスタ数を表にまとめたところ、ちょうど工学解析のように、いくつか内部的に食い違いが生じました。分かったのは、業界標準の方法でカウントするツールでは、私たちがこれまでそうしてきたのに比べて、トランジスタ数が多くカウントされるということでした。」

従来のカウント方法と新しいカウント方法との間での食い違いの多くは、少なくともPower10およびPower11については、デキャップ セル(デカップリング コンデンサ セルの略)と呼ばれるものに由来しているようです(デキャップ セルは、CMOSトランジスタで構成され、回路の近くに配置して電力を貯蔵し、電力供給を安定化させ、チップの入力信号のノイズを低減するのに使用されます)。

サーバー チップ デザインについてざっと検索してみたところでは、一般にサーバー チップの場合、デキャップ セルの数は、かつてはトランジスタの総数に対してわずかな割合を占めるに過ぎませんでしたが、今日のより先端的なノード(5ナノメートル プロセス)では5%に達することもあるということです。キャッシュ メモリー(チップのL1、L2、およびL3キャッシュの階層に応じて)と、プロセッサーの構成要素をネットワークするのに使用されるチップの「非コア」領域で、総トランジスタ数の65%~80%程度を占めることがあるようです。残りの15%~35%は、プロセッサー コア、コントローラー、およびアクセラレーターが占めます。

デキャップ セルの数は約120億個だという新たなデータがあります。これは総トランジスタ数の約5%ではなく、約40%に相当することになります。だとすると、IBMがPowerチップ デザインで、いかにうまくパワー ゲーティングやパワー デリバリーを行うことができるかということや、さらには、いかにうまく、 N プロセスでクロック スピードを4 GHz~5 GHzに押し上げることができるかということは、このことである程度、説明が付くのかもしれません(ちなみに他社は N+1 プロセスのサーバーCPUで3 GHzに到達するのに苦戦しているようです)。

デキャップ セルは、IBMのチップ デザイナーにとっての戦略的メリットということになるのかもしれません。

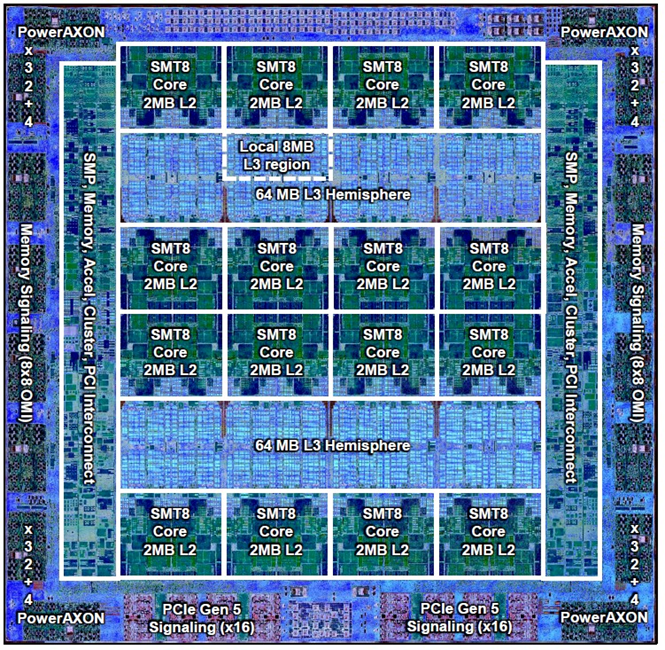

これらのデキャップ セルは、Power10およびPower11デザインの至る所にまんべんなく分散されているのでしょうが、チップ ブロック図でその姿を確認することはできないでしょう。Power10のブロック図を見てみましょう。基本的にPower11と同じです。

チップ画像上に描かれている、チップ ブロックを区分けしている白い線が回路のサイズと比べてかなり太めだということは踏まえた上で、どのように区分けされているかに基づいてざっくり推定してみれば、チップ面積全体の約85%は、L1、L2、およびL3キャッシュ用だということが分かるでしょう。約10%がコア ロジック用で、I/Oコントローラー、メモリー コントローラー、およびオンチップ インターコネクトがおそらく5%を占めます。ここで合理的な推定だと言えるのは、デキャップ セルがチップ全体に分散されているということだけかもしれません。

では、さらに踏み込んで、一番妥当性の高そうな推定を行ってみるとすれば、Power11には300億個のトランジスタがあり、約150億個がL1、L2、およびL3キャッシュで使用され、120億個がデキャップ セル、約20億個がCPUコア(もちろんL1およびL2キャッシュの分は差し引いて)、約10億個がI/Oおよびメモリー コントローラー、およびオンチップ インターコネクトで使用されるということになるでしょうか。この推定が合理的であるためには、Power11チップは、Power10に比べてまさしく52 mm2 だけ大きく、歩留りを何とか改善するべく修正された7ナノメートル プロセスを使用していたか、デキャップ セルがもっと多いか、あるいは、私たちが知らない隠れたフィーチャーが他にあるかのいずれかということになります。Power10に比べてPower11は面積が広く、トランジスタ数が多いとすれば、Power11のデキャップ セルはさらに多いということもあり得ます。面積およびトランジスタ数から逆算してみると、Power10のデキャップ セルの数は、Power11で使用されている120億個ではなく、110億個ということになるでしょう。

もちろん、これは単なる推測に過ぎません。しかし、分かっていることは、Power10とPower11との間で、トランジスタ数もチップ面積もあまり変わっていないということ、そしてそれらは非常によく似たチップであり、マイクロアーキテクチャーの微調整が少し施され、電力分配システムが大幅に改善されているということです。それについては、来週の記事で取り上げようと思います。